SPI、DSPI、QSPI 笔记

SPI、DSPI、QSPI 笔记

nixgnauhcuy1 前言

复习下,SPI、DSPI、QSPI 对应的接口时序,并作笔记。

2 SPI

2.1 简介

SPI(Serial Peripheral Interface),是一种同步串行通信协议,用于在微控制器与各种外围设备进行全双工通信,它是一种全双工通讯协议,意味着数据可以同时在两个方向上传输。它是由摩托摩拉公司设计。

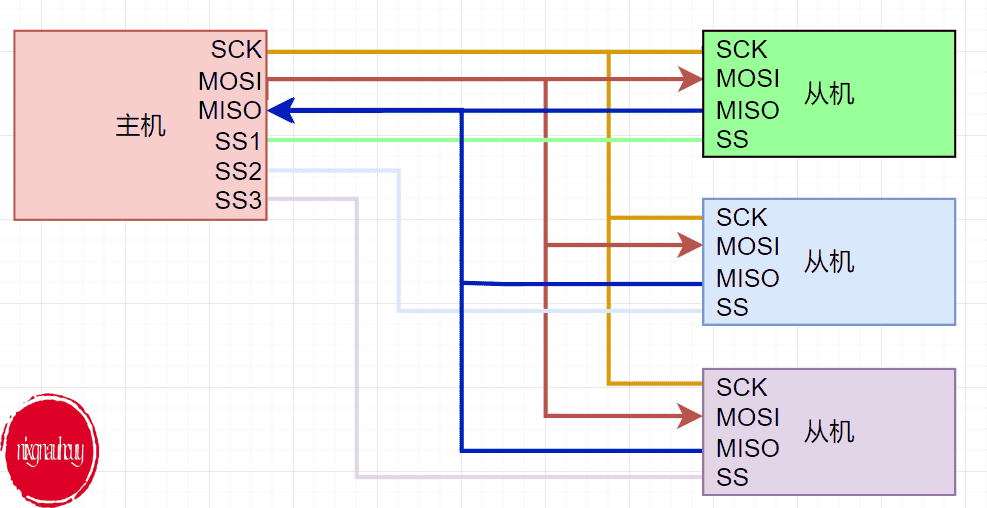

SPI 协议通常由一个主设备(主机)和一个或多个从设备(从机)组成。主设备负责发起通信并控制数据传输的时序,而从设备则被动地响应主设备的指令并提供数据。

2.2 接口

SPI 通信涉及四条线:

- SCLK:串行时钟(Serial Clock),由主设备产生,用于同步数据传输。

- MOSI:主出从入(Master Out Slave In),用于从主设备向从设备传输数据。

- MISO:主入从出(Master In Slave Out),用于从从设备向主设备传输数据。

- SS(或CS):片选(Slave Select),主设备用来选中特定的从设备进行通信。

SPI 协议的工作方式是通过主设备产生时钟信号来同步数据传输。主设备通过 SCLK 线产生时钟脉冲,每个时钟脉冲对应一个数据位的传输。在每个时钟脉冲期间,主设备将一个数据位发送到 MOSI 线上,同时从设备将一个数据位发送到 MISO 线上。通过这种方式,主设备和从设备可以同时传输数据。

2.3 时序

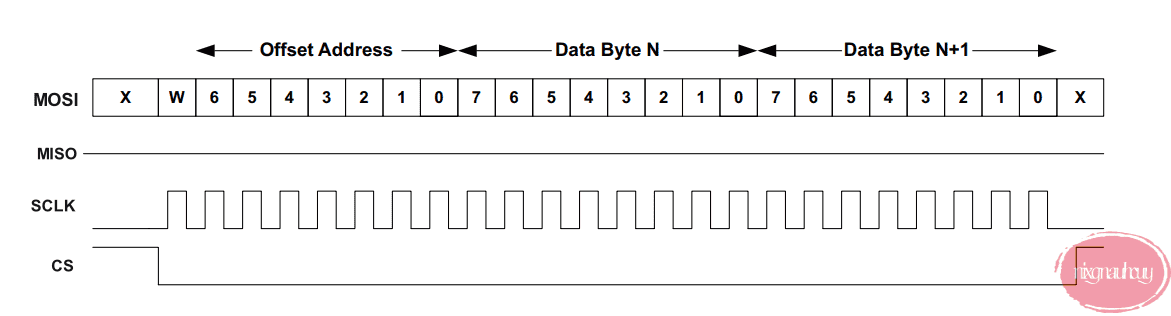

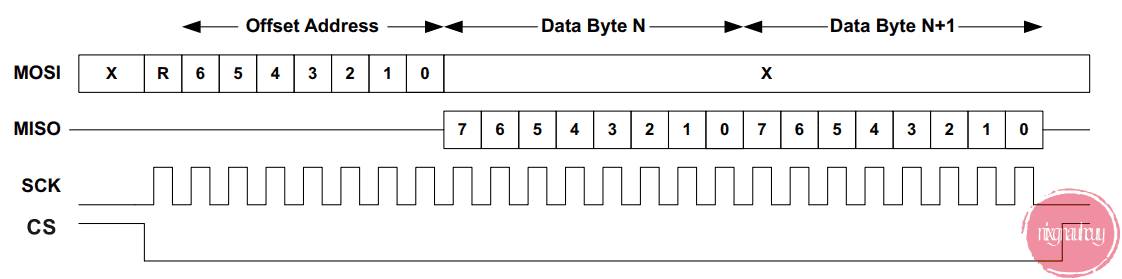

2.3.1 读时序

2.3.2 写时序

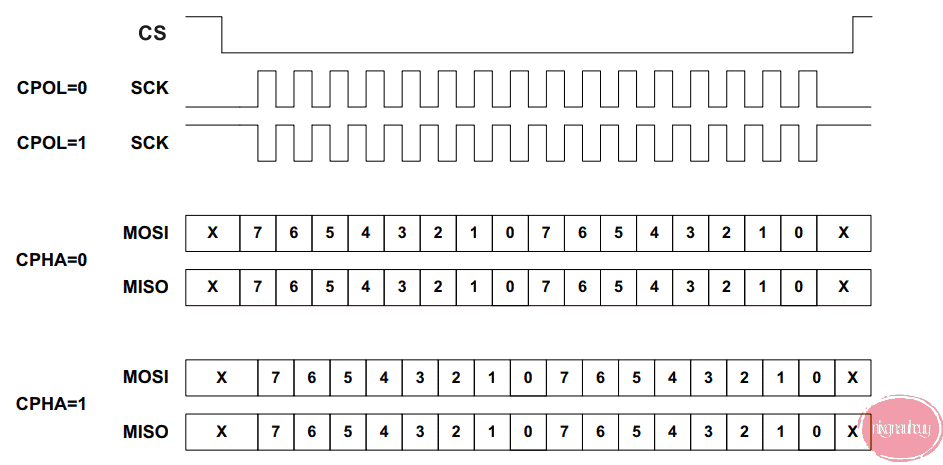

2.4 模式

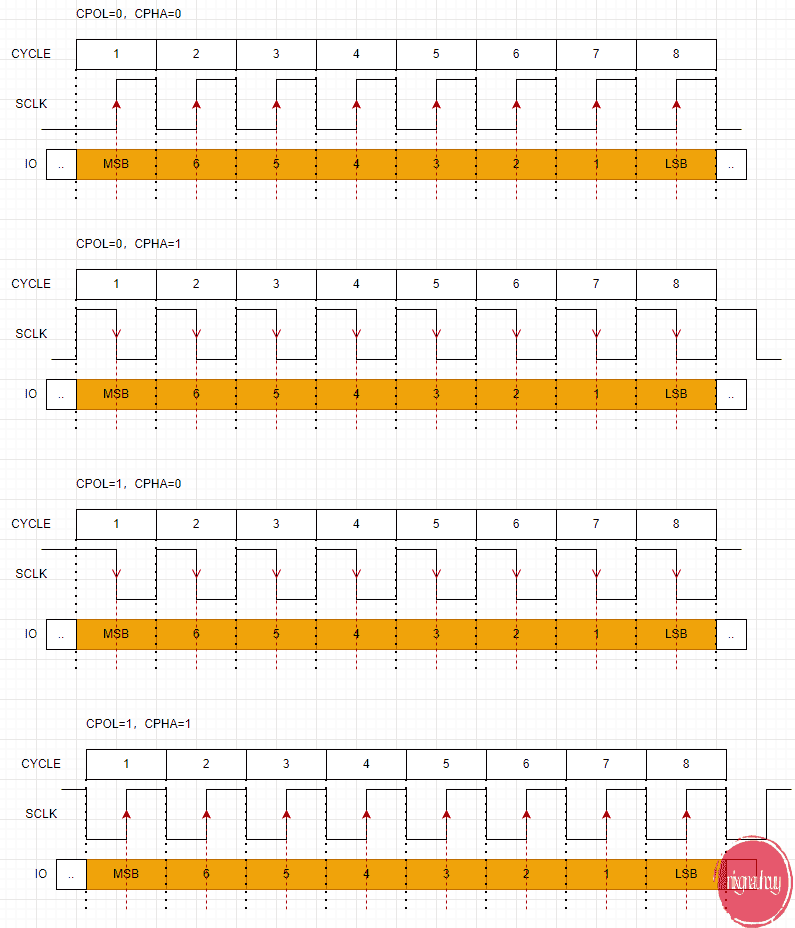

认识四种模式前,需要先了解两个概念:

- Clock Polarity - 时钟极性,用来描述 SCLK 时钟信号空闲状态的电平,0:低电平 1:高电平。

- Clock Phase - 时钟相位,一个时钟周期会有 2 个跳变沿,相位用来规定 SCLK 时钟信号是第一个跳变沿有效还是第二个跳变沿有效,0:第一个跳变沿 1:第二个跳变沿。

| MODE | CPOL(Clock Polarity) | CPHA(Clock Phase) | NOTE |

|---|---|---|---|

| mode 0 | 0 | 0 | SCLK 空闲电平为低并且相位是一个跳变沿有效,那么说明是上升沿有效 |

| mode 1 | 0 | 1 | SCLK 空闲电平为低并且相位是二个跳变沿有效,那么说明是下降沿有效 |

| mode 2 | 1 | 0 | SCLK 空闲电平为高并且相位是一个跳变沿有效,那么说明是下降沿有效 |

| mode 3 | 1 | 1 | SCLK 空闲电平为高并且相位是二个跳变沿有效,那么说明是上升沿有效 |

3 DSPI

3.1 简介

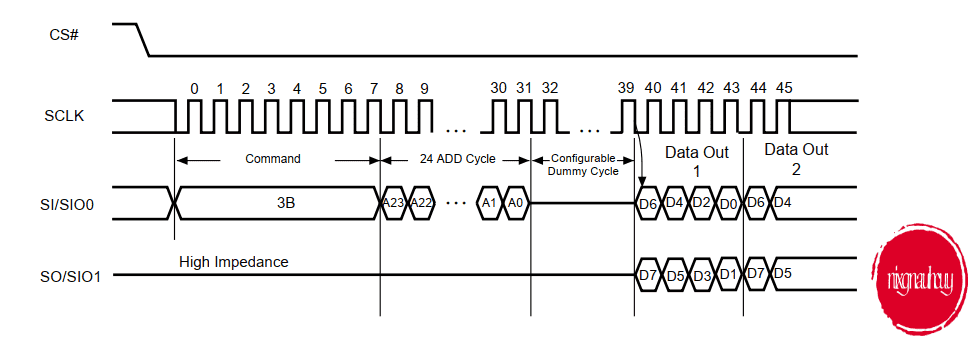

DSPI(Dual Serial Peripheral Interface),是 SPI 的一种扩展,在不使用 SPI 全双工性质的情况下,扩展使用半双工配置的两个数据引脚,在每个时钟周期发送两位。

它将 MOSI 线变成 SIO0、MISO 变为 SIO1,分别携带偶数位和奇数位,例如 SIO0 携带每个字节的位 6、4、2 和 0,SIO1 携带字节的位 7、5、3 和 1。

3.2 接口

DSPI 通信涉及四条线:

- SCLK:串行时钟(Serial Clock),由主设备产生,用于同步数据传输。

- SIO0(MOSI):Data Input Output 1。

- SIO1(MISO):Data Input Output 2。

- SS(或 CS):片选(Slave Select),主设备用来选中特定的从设备进行通信。

3.3 时序

上述流程为:

CS 拉低 -> 发送指令(3B) -> 发送地址(A0-A23,24 位地址) -> 等待 8 个空指令周期 -> 数据阶段,开始双线发送任意数量字节

4 QSPI

4.1 简介

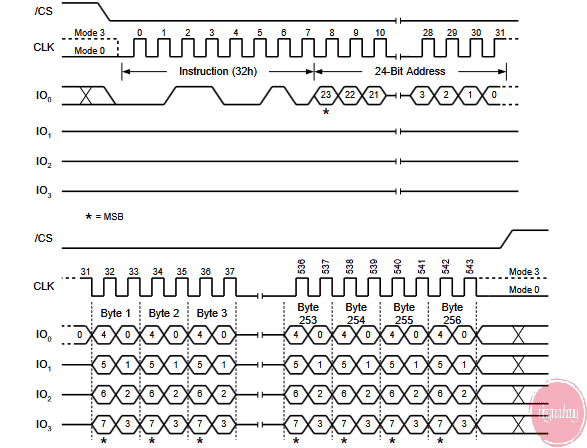

QSPI(Quad Serial Peripheral Interface),同样是 SPI 的扩展,进一步的提高了传输速度,数据可以通过四条数据线同时传输,因此,在每个时间周期可以传输四个数据位。

4.2 接口

QSPI 通信涉及六条线:

- SCLK:串行时钟(Serial Clock),由主设备产生,用于同步数据传输。

- IO0,IO1,IO2,IO3:四条 Input Output Data 线。

- SS(或 CS):片选(Slave Select),主设备用来选中特定的从设备进行通信。

4.3 时序

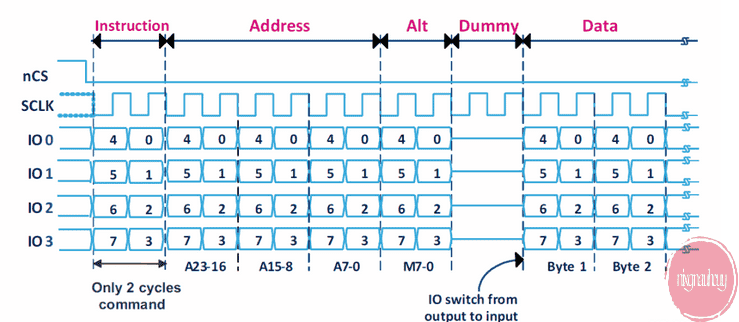

上述是一个典型的 QSPI 时序,工作模式切换到 QSPI 四线模式后,大致流程如下:

1 | 指令(Instruction) + 地址(Address) + 扩展信息(Alt) + Dummy Clock(空闲周期) + 数据(Data) 。 |